Reg No.:

Name:

# APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

B. Tech Degree S3 (R) (FT/WP) Examination November 2025 (2024 Scheme)

2024 Scheme)

**Course Code: PCECT303**

**Course Name: ANALOG CIRCUITS**

Max. Marks: 60

Duration: 2 hours 30 minutes

# PART A

|   | (Answer all questions. Each question carries 3 marks)                                              | CO | Marks |

|---|----------------------------------------------------------------------------------------------------|----|-------|

| 1 | Explain why a fixed bias circuit is not widely used in amplifiers, despite its simplicity.         | 2  | (3)   |

| 2 | Design a low pass filter for a cutoff frequency of 5KHz.                                           | 1  | (3)   |

| 3 | Draw the frequency response of a CE amplifier. What is the significance of gain bandwidth product? | 2  | (3)   |

| 4 | Explain the impact of the Miller effect on the frequency response of an amplifier.                 | 2  | (3)   |

| 5 | Deduce the expression for closed loop gain $A_{\rm f}$ of a negative feedback amplifier.           | 1  | (3)   |

| 6 | Explain the criteria for sustained oscillations.                                                   | 1  | (3)   |

| 7 | Why class AB power amplifiers are preferred over class B operations?                               | 2  | (3)   |

| 8 | Define line regulation and load regulation, and discuss their importance in power supply design.   | 1  | (3)   |

|   |                                                                                                    |    |       |

### PART B

(Answer any one full question from each module, each question carries 9 marks)

#### Module -1

- 9 a) What is thermal runaway? Explain the role of emitter resistance R<sub>E</sub> in the 1 (5) potential divider biasing circuit.

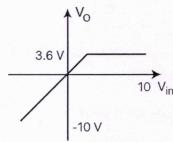

- b) Design a clipper circuit to obtain the following transfer characteristics. 1 (4)

- a) Obtain the operating point set by the voltage divider bias circuit for an 2 (5) NPN transistor in common emitter configuration with  $\beta$  = 50 and  $V_{BE}$  = 0.7 V. Given Vcc = 12V,  $R_1$ =47kΩ,  $R_2$ =10KΩ,  $R_2$ =2.2KΩ and  $R_E$ = 680Ω.

- b) Design a clamper circuit to clamp a 10Vpp sine wave so that positive peak 1 (4) is clamped at -3V. Draw the output waveform and transfer characteristics.

Assume diode is ideal.

### Module -2

- 11 a) Draw and explain the circuit of RC coupled amplifier and draw its frequency 2 (5) response curve.

- b) Draw and explain the Common Source MOSFET amplifier. 2 (4)

- 12 a) Draw the small signal low frequency hybrid  $\pi$  model for common emitter 2 (5) configuration. Give the expression for voltage gain, input and output impedance.

#### 06PCECT303112501

b) Three stages of individual RC coupled amplifier having mid-band gain of 80 (4) with lower cut-off frequency of 100Hz and upper cut-off frequency of 300MHz are cascaded. Find the resultant gain and cut-off frequencies. Module -3 13 With necessary diagram, explain the working of crystal oscillator. 2 (5) a) b) Explain voltage series feedback topology with neat block diagram. Derive 2 (4) the expression for net input and output impedance. Draw the circuit of Wien bridge oscillator. Derive the expression for its 14 a) (5)frequency of oscillation. Explain the effect of negative feedback on gain, bandwidth, stability and 2 b) (4) distortion in feedback amplifiers. Module -4 15 Explain the working of series voltage regulator. 1 (5) a) 2 What is cross over distortion? How can it be overcome? (4) b) 16 What is a Class B push-pull power amplifier? With necessary diagram 2 (5) a) Explain its working. With necessary diagram, explain the working of shunt voltage regulator. 1 (4)

\*\*\*