### APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

B.Tech Degree S5 (S, FE) / S3 (PT) (S) Examination June 2024 (2019 Scheme)

# Course Code: ECT 301 Course Name: LINEAR INTEGRATED CIRCUITS

Max. Marks: 100 Duration: 3 Hours

#### PART A

(Answer all questions; each question carries 3 marks)

Marks

- Draw the equivalent circuit of an op-amp and list the component values of the 3 modelled circuit to work as an ideal op-amp.

- Find the maximum possible frequency, without distortions, for a sine wave of 3 voltage 12V peak to peak with an op-amp whose slew rate is 10V/μs.

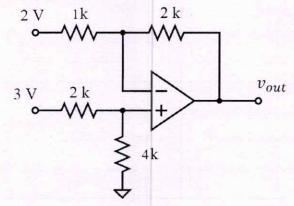

- 3 Calculate Vout for the circuit shown below.

3

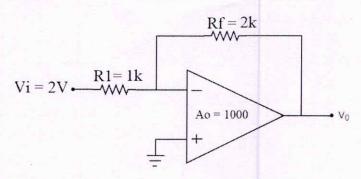

Find Vo, if open loop gain of the below op-amp is 1000.

3

5 How Barkhausen criteria is achieved in RC phase shift oscillator?

3

6 List the advantages of an Op-amp based active filter over conventional passive 3 filters.

#### 1100ECT301122101

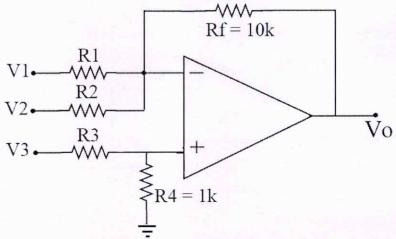

7 What does NE and 555 in NE555 timer IC stands for? 3 8 Design a monostable multivibrator using 555 to get a pulse width of 10ms. 3 9 Explain Line regulation and Load regulation. 3 10 Find the resolution of a 10 bit ADC with 5V full scale reading. 3 PART B (Answer one full question from each module, each question carries 14 marks) Module -1 Explain the principle of operation of Widlor current mirror and its advantages? 11 8 Deduce the expression for its current gain. b) Draw and explain the voltage transfer curve and frequency response curve of an 6 op-amp. 12 a) Derive CMRR, input resistance and output resistance of a dual input balanced output 8 differential amplifier configuration. b) Explain the following properties of a practical opamp 6 (i) Bandwidth (ii) Slew rate (iii) Input offset voltage (iv) CMRR Module -2 8 13 a) Derive the following characteristics of a voltage series amplifier: i) Closed loop voltage gain ii) Input resistance iii) Output resistance iv) Bandwidth b) Find the values of resistors R1,R2 and R3 so that  $V_0 = -10 \text{ V}1 - 5 \text{ V}2 + 4 \text{ V}3$

14 a) With necessary equations and waveforms explain the working of a schmitt 8 trigger circuit with different values for upper and lower threshold. Also design such a Schmitt trigger circuit with  $V_{UT} = 9V$  and  $V_{LT} = -7V$ . Assume saturation voltage levels as 12V and -12V.

## 1100ECT301122101

|    | b) | Draw and explain precision full wave rectifier circuit. Include equivalent circuits  | 0 |

|----|----|--------------------------------------------------------------------------------------|---|

|    |    | for positive and negative half cycles.                                               |   |

|    |    | Module -3                                                                            |   |

| 15 | a) | Draw and explain the working of an op-amp based RC phase shift oscillator.           | 8 |

|    |    | Also derive the equation for frequency of oscillation.                               |   |

|    | b) | Draw the circuit of a state variable filter and derive the transfer function of high | 6 |

|    |    | pass filter response in it.                                                          |   |

| 16 | a) | Draw and explain the working of an op-amp based triangular wave generator.           | 8 |

|    |    | Also derive the equation for frequency of oscillation.                               |   |

|    | b) | Design a 50Hz twin- T notch filter with a Q factor of 15.                            | 6 |

|    |    | Module -4                                                                            |   |

| 17 | a) | Using internal diagram of NE555 IC, explain the working of symmetric astable         | 7 |

|    |    | multivibrator circuit.                                                               |   |

|    | b) | Using internal block diagram of NE 566 explain the working of VCO.                   | 7 |

| 18 | a) | Using internal diagram of NE555 IC explain the working of monostable                 | 7 |

|    |    | multivibrator circuit. Write the necessary condition for the trigger voltage level?  |   |

|    | b) | Explain the working of Phase Locked Loop and its application as a frequency          | 7 |

|    |    | multiplier circuit.                                                                  |   |

|    |    | Module -5                                                                            |   |

| 19 | a) | Explain how external current fold back protection is achieved while designing        | 7 |

|    |    | voltage regulator using IC 723.                                                      |   |

|    | b) | Find the output voltage for the following DACs having an output voltage range        | 7 |

|    |    | of 0 to 10V.                                                                         |   |

|    |    | i) 0110 for a 4 bit DAC                                                              | 0 |

|    |    | ii) 10111100 for an 8 bit DAC                                                        |   |

|    |    | iii) 1010100011 for a 10 bit DAC                                                     |   |

| 20 | a) | Design a voltage regulator using IC 723 for an output voltage of 5V and current      | 7 |

|    |    | of 2A. Assume Vref = 7V. Also explain how line regulation is achieved in it.         |   |

|    | b) | With a neat diagram explain the working of successive approximation type ADC         | 7 |