Name:

# APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Sixth Semester B.Tech Degree (R,S) Examination May 2024 (2019 Scheme)

019 Scheme EDUCATION

Course Code: ECT312

Course Name: DIGITAL SYSTEM DESIGN

Max. Marks: 100 Duration: 3 Hours

#### PART A Answer all questions, each question carries 3 marks. Marks 1 Differentiate between Mealy and Moore models. (3) 2 List out the steps in state table reduction using implication chart method. (3) 3 What is fundamental mode in asynchronous sequential circuits? (3) 4 In asynchronous sequential circuits, how does a state table differ from a flow (3) table? 5 Define clock skew. Explain the different types. (3) 6 Differentiate between synchronous and asynchronous inputs of a sequential (3) circuit. 7 List the different types of faults in digital circuits. (3) 8 Distinguish between essential, selective and redundant test vectors in fault (3) detection. 9 Differentiate between CPLD and FPGA. (3) 10 What is configurable logic block in FPGA? (3) PART B Answer one full question from each module, each question carries 14 marks. Module I Design a clocked synchronous sequential Moore network to detect the overlapping 11 a) (7) sequence of 110 using D flipflop. b) Using implication chart, construct the minimal state table from the state table (7)given below.

| Present state | Next state Input(x) |   | output<br>Input(x) |   |

|---------------|---------------------|---|--------------------|---|

|               |                     |   |                    |   |

|               | A                   | В | С                  | 0 |

| В             | С                   | D | 1                  | 0 |

| С             | В                   | Е | 0                  | 0 |

| D             | F                   | Е | 0                  | 0 |

| Е             | G                   | A | 0                  | 0 |

| F             | F                   | Н | 1                  | 0 |

| G             | A                   | D | 1                  | 0 |

| Н             | D                   | F | 1                  | 1 |

|               | Con-                |   |                    |   |

OR

- 12 a) Draw the ASM chart for a Serial Binary Adder as Mealy Network. (6)

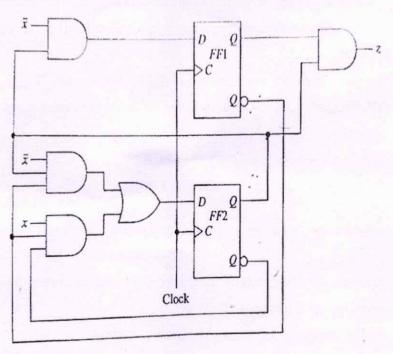

- b) Analyse the following clocked synchronous sequential network. Construct the

excitation table, transition table, state table and state diagram.

Module II

- 13 a) Explain races in asynchronous sequential circuits with the aid of a suitable (6) example.

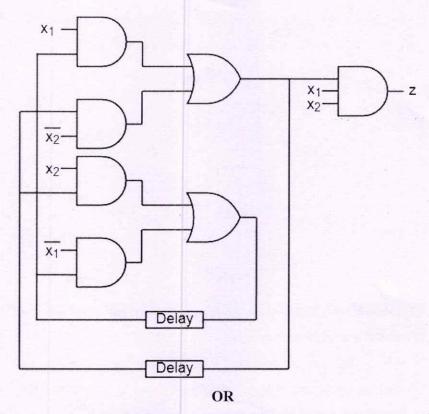

- b) Examine the Asynchronous Sequential Circuit shown below to generate the excitation/transition table, state table, flow table and flow diagram.

- Define a primitive flow table. Establish a primitive flow table for designing an (14)

Asynchronous Sequential Circuit which meets the following requirements:

- (i) There are 2 inputs x1 and x2 and single output z.

- (ii) The inputs x1 and x2 never change simultaneously.

- (iii) The output is always to be 0, when x1 = 0, independent of the value of x2.

- (iv) The output is to become 1 if x2 changes while x1=1 and is to remain 1 until x1 becomes 0 again.

Also obtain the reduced flow table by applying the flow table reduction techniques.

## Module III

- 15 a) Explain the problem of contact bounce in switches and show how an SR latch can (7) eliminate the problem by suitable illustrations.

- b) With a suitable circuit and waveforms, explain the functioning of a Data (7)

Synchronizer.

OR

### 1200ECT312012401

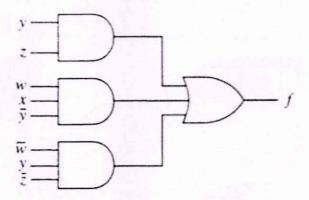

16 a) For the gate network shown in figure, determine all the static 1 & static 0 hazards. (8)

Redesign the network to be hazard free and having the same output gate as in figure.

b) Explain essential hazards in asynchronous sequential networks and how it can be avoided in a sequential circuit.

### Module IV

- 17 a) A circuit realizes the function z=x<sub>1</sub>'x<sub>4</sub>+x<sub>2</sub>'x<sub>3</sub>+x<sub>1</sub>x<sub>4</sub>'. Using the Boolean difference (8) method, find the test vectors for SA0 faults and SA1 faults on the input line x<sub>1</sub> of the circuit.

- b) Write a note on Automatic Test Pattern Generation.

OR

- a) Illustrate the fault table method used for effective test set generation for the circuit (8) whose Boolean function is z = x1'x2+x3 and find the minimal test set. Identify the redundant test vector.

- b) Write a note on BIST techniques.

## Module V

OR

- 19 a) With a suitable diagram, describe the input-output block architecture of Xilinx9500 CPLD family.

- b) Explain the architecture of XC 4000 FPGA family.

(7)

(6)

(6)

(7)

20

- a) Explain switch matrix in Xilinx XC9500 CPLD. (7)

- b) Using suitable illustrations explain the XC4000 programmable interconnect.

(7)

\*\*\*\*