# 03000EE365092001

F

-2

Reg No.:\_

Name:

Po.

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

Fifth semester B.Tech degree examinations (S) September 2020

# Course Code:EE365

## Course Name: DIGITAL SYSTEM DESIGN

| Max. Marks: 100 Duration: 3 Hours |                                                                                    |       |  |

|-----------------------------------|------------------------------------------------------------------------------------|-------|--|

|                                   | PART A<br>Answer all questions, each carries5 marks.                               | Marks |  |

| 1                                 | Define Design Automation and explain the tasks to be performed by EDA              | (5)   |  |

|                                   | tools?                                                                             |       |  |

| 2                                 | Explain the basic structure of VHDL Code?                                          | (5)   |  |

| 3                                 | With the help of suitable block diagram explain the different models of            | (5)   |  |

|                                   | synchronous sequential systems?                                                    |       |  |

| 4                                 | Write VHDL code for negative edge T-FF?                                            | (5)   |  |

|                                   | (Assume Necessary data if Required)                                                |       |  |

| 5                                 | Explain VHDL simulation cycle?                                                     | (5)   |  |

| 6                                 | With the help of suitable example, explain the concept of inferred Latch in        | (5)   |  |

|                                   | synthesis of process statements                                                    |       |  |

| 7                                 | With the suitable diagram describe four types of cross point fault that can occur  | (5)   |  |

|                                   | in a PLA consisting of AND and OR Plane                                            |       |  |

| 8                                 | With the help of suitable diagram explain the architecture of Built in logic block | (5)   |  |

|                                   | observation (BILBO)                                                                |       |  |

|                                   | PART B<br>Answer any two full questions, each carries 10 marks.                    |       |  |

| 9 a)                              | Explain the basic architecture of FPGA?                                            | (5)   |  |

| b)                                | Compare signal and variable in VHDL?                                               | (5)   |  |

| 10                                | Explain the role of Test bench in VHDL? Write VHDL test bench to test all          | (10)  |  |

|                                   | combination of 8:1 Multiplexer?                                                    |       |  |

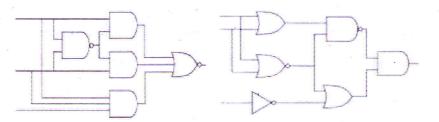

| 11                                | Derive Boolean expressions for the circuits of Figure shown below; use truth       | (10)  |  |

|                                   |                                                                                    |       |  |

tables to discover if they are equivalent. Assume inputs A, B, & C.

### 03000EE365092001

### PART C

|    |    | Answer any two full questions, each carries 10 marks.                         |      |

|----|----|-------------------------------------------------------------------------------|------|

| 12 |    | Derive state diagram and hence draw the ASM chart for mod-6 counter           | (10) |

|    |    | (Assume Necessary data if Required)                                           |      |

| 13 |    | With the help of necessary timing diagram explain the operation of dynamic    | (10) |

|    |    | RAM and hence write its VHDL Code?                                            |      |

| 14 | a) | Explain the salient features of ASM chart                                     | (5)  |

|    | b) | Identify the circuit that can generate the following sequence and hence write | (5)  |

|    |    | VHDL code for obtaining the same (Assume Necessary Data, if required)         |      |

|    |    | "1000","1100","1110","1111","0111","0011","0001","0000",                      |      |

|    |    | PART D                                                                        |      |

|    |    | Answer any two full questions each carries 10 marks                           |      |

#### Answer any two full questions, each carries 10 marks.

The following sequence of operations is part of a cube root solution routine: (10) $a \le x * x;$

a <= 3 \* a;

$b \leq y/a;$

$a \le a / 3;$

$c \leq a - b;$

Convert this sequence to single assignment form and hence construct a data dependency graph. Assuming that each arithmetic operation takes exactly one clock cycle, derive an unconstrained as late as possible (ALAP) schedule.

16

15

1

- What are different styles of design that should be avoided and different (10)modifications methods to enhance the testability of that design?

- 17 a) With the help of suitable example explain resources constraints during (5) synthesis?

- b) Explain the phases involved in path sensitization based automatic test pattern (5) generation (ATPG) scheme.

\*\*\*\*

Page 2 of 2