C192056

Reg No.:

Name:

# APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY THIRD SEMESTER B.TECH DEGREE EXAMINATION(R&S), DECEMBER 2019

### **Course Code: EC207**

## **Course Name: LOGIC CIRCUIT DESIGN**

Max. Marks: 100

**Duration: 3 Hours**

(4)

Pages:3

## PART A Marks Answer any two full questions, each carries 15 marks. 1 a) Two numbers A & B in Hex are given A = 85CA, B = 23C6(10)Find the Decimal equivalent of A & B i. ii. Find the binary of A & B iii. What is the sum of A& B in HEX b) Write down the algorithm for BCD Addition. Find the sum of numbers 74998 and (5)38976 by BCD addition. Show the steps clearly. 2 Express f = AB + AC + C + AD + ABC + ABC in standard SOP form. a (7)Using K map simplify the SOP function, and realize it using logic gates. b (8) $f(a,b,c,d) = \Sigma m (0,1,2,4,5,6), \quad d = \Sigma (3,7,14,15)$ a) Realize a XNOR circuit using NAND gate only. (6) 3 b) A logic circuit has our inputs A,B,C and D. A four bit input is fed with A as MSB (9) and D as LSB. Design and implement a circuit such that the output is one when the input is more than or equal to decimal 6. PART B Answer any two full questions, each carries 15 marks. (7)a) Realize a 3 bit gray to binary decoder using PROM. Give all details. 4 b) What is meant by race around condition? How it is eliminated. Illustrate with the (8) help of necessary sketches. 5 a) Convert a JK flipflop into a D flipflop, (7)b) Design and implement a circuit for generating the sequence 2-5-7-3-0 (8)

# 6 a) Define the following

(i) Fan out

#### Page 1 of 3

E

C192056

Pages:3

(3)

(10)

- (ii) Fan in

- b) What is the difference between a latch and a flipflop.

- c) Design an asynchronous 3 bit up counter. Write complete truth table and (8) excitation table.

## PART C

## Answer any two full questions, each carries20 marks.

- 7 a) A register is to be designed, which provides all the following functions shift left, (10) shift right, parallel in, parallel out, serial in, serial out, serial in parallel out and parallel in serial out. Draw the circuit for a 4 bit data (serial/parallel) and provide its working.

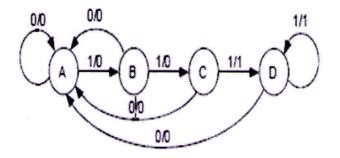

- b) Draw the Mealy machine for the given table.

| Present | Next state, output |   |         |   |  |

|---------|--------------------|---|---------|---|--|

| state   | x=0                |   | x=1     |   |  |

| Y1 Y0   | y1 y0 /            | Z | y1 y0 / | Z |  |

| 00      | 01,                | 0 | 10,     | 0 |  |

| 01      | 01,                | 1 | 10,     | 0 |  |

| 10      | 01,                | 0 | 11,     | 0 |  |

| 11      | 01,                | 0 | 11,     | 1 |  |

- 8 a) Draw the logic diagram of a Johnson counter. Why it is called a divide by 2N (8) counter. Draw the neat diagram of clock and output waveforms of a 4 bit Johnson counter.

- b) Use the state reduction technique and implement the circuit for the given state (12) diagram.

Page 2 of 3

E

C192056

# Pages:3

(10)

9 a) Design a mealy machine to detect an input sequence10110. The system should be (10) able to detect overlapped sequence. Also draw the state diagram

\*\*\*\*

b) Obtain a minimum row primitive flow table for the state table shown below.

|    | 00  | 01             | X <sub>2</sub> | 10  | Z <sub>1</sub> Z <sub>2</sub> |

|----|-----|----------------|----------------|-----|-------------------------------|

| 1  |     | 7              | -              | 4   | 11                            |

| 2  | 2   | 5              | -              | 4   | 01                            |

| 3  | -   | 7              | (3)            | 11  | 10                            |

| 4  | 2   | -              | 3              | (4) | 00                            |

| 5  | 6   | (5)            | 9              | -   | 11                            |

| 6  | (6) | 7              |                | 11  | 01                            |

| 7  | 1   | $\overline{O}$ | 14             | -   | 10                            |

| 8  | (8) | 12             |                | 4   | 01                            |

| 9  | -   | 7              | (9)            | 13  | 01                            |

| 10 |     | 7              | 60             | 4   | 10                            |

| 11 | 8   |                | 10             | (1) | 00                            |

| 12 | 6   | (12)           | 9              | -   | 11                            |

| 13 | 8   | -              | 14             | (3) | 11                            |

| 14 | -   | 12             | (14)           | 11  | 00                            |

E