Name.... Reg. No....

## FIFTH SEMESTER B.TECH. (ENGINEERING) DEGREE **EXAMINATION, DECEMBER 2010**

EE 04 503 PULSE AND DIGITAL ELECTRONICS

Time: Three Hours

Maximum 100 Marks

- I. (a) Explain Miller Sweep circuit using op-amp.

- (b) Explain forward and reverse recovery of diodes.

- (c) Explain Multiplexer with a neat diagram.

- (d) Explain half-adder and draw its logic diagram.

- (e) Draw the excitation table and Truth table for JK flip-flop.

- (f) Explain Dynamic RAM with a neat diagram.

- (g) Write any five multibyte instructions.

- (h) Explain control bus with a neat diagram.

$(8 \times 5 = 40 \text{ marks})$

II. (a) (i) Explain resistive and clamped inductive switching of BJT.

(8 marks)

(ii) Explain collector coupled Astable transistor Schmitt Trigger circuit with a neat diagram.

nergaib teen a driv 2808 to embediante ed niclay (7 marks)

(b) Explain the switching behaviour of diode with a neat diagram. (15 marks)

III. (a) (i) Reduce the following function using K-map technique:

falson  $00 = 01 f(A, B, C, D) = \sum m(0, 1, 4, 8, 9, 10).$

(8 marks)

(ii) Define PLA and compare PLA with PAL.

(7 marks)

Or

(b) Explain Mux and Demux with an example.

(15 marks)

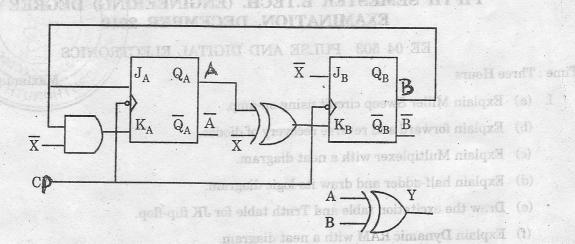

## IV. (a) Derive the state table and state diagram for sequential circuit shown in figure.

mergaib taen a driw and lorinos austro (15 marks)

Or

(b) (i) Draw the Excitation table and truth table of JK flip-flop. (8 marks)

(ii) Explain Johnson counter with a neat diagram. (7 marks)

V. (a) Explain the architecture of 8085 with a neat diagram.

01

(b) (i) Write short notes on flags in 8085 processor.

(b) Explain the switching behaviour of (akram 8)

(ii) Explain arithmetic logic unit with a neat diagram.

(7 marks)

(0.0834.10) m  $(=0.08.44 \times 15 = 60 \text{ marks})$

(8 marks)

$(8 \times 5 = 40 \text{ marks})$

(ii) Define PLA and compare PLA with PAL.

(b) Explain Mux and Demux with an example.

gevo mull